Industria cipurilor logice se îndreaptă spre o schimbare fundamentală a structurii tranzistoarelor. Tranzistoarele din prezent, denumite FinFET, vor fi înlocuite de dispozitive denumite tranzistoare nanosheet (nanofoi), FET-uri cu canale multibridge și tranzistoare gate-all-around. În plus, față de dorința de realizare a unor tranzistoare mai performante și de dimensiuni mai reduse, nanosheet-urile adaugă un grad de libertate proiectării circuitelor, caracteristică pe care FinFET-urile nu îl au. La începutul lunii martie 2021, în cadrul Conferinței Internaționale a Circuitelor în Stare Solidă IEEE, inginerii din cadrul companiei Samsung au arătat modul în care această flexibilitate suplimentară conduce la dezvoltarea unor celule de memorie de tip on-chip, care pot fi realizate folosind un potențial mai mic cu sute de milivolți decât cele existente, astfel, economisindu-se mai multă energie.

Deși compania Taiwan Semiconductor Manufacturing Co. (TSMC) intenționează să producă FinFET-uri și pentru generația următoare de dispozitive, bazate pe un proces de fabricație pe 3 nanometri, Samsung va introduce versiunea proprie de nanosheeturi, mai exact MOSFET-uri cu canale multibridge (MBCFET). În cazul FinFET-urilor, regiunea de canal, adică partea tranzistorului prin care trece curentul, este formată dintr-o aripă verticală care iese din stratul de siliciu din jur. Poarta acoperă aripa pe trei laturi pentru a controla fluxul de curent prin canal. Nanosheet-urile înlocuiesc aripa cu un set de foi orizontale de siliciu. Poarta înconjoară complet fiecare foaie.

„Am utilizat tranzistoare FinFET timp de aproximativ un deceniu. Cu toate acestea, în cadrul procesului de fabricație pe 3 nm, folosim o poartă care înconjoară întregul tranzistor. Noul tranzistor asigură o viteză mai mare, un consum de energie mai mic și o dimensiune redusă”, a declarat vicepreședintele Samsung Electronics, Taejoong Song, în cadrul conferinței virtuale.

Noua structură a dispozitivului adaugă un grad de flexibilitate de proiectare de care nu beneficiază FinFET-urile. Factorul acestei flexibilități este reprezentat de „lățimea efectivă” sau Weff-ul canalului tranzistorului. În general, un canal mai mare poate conduce mai mult curent prin el la o anumită tensiune, reducându-se, efectiv, rezistența acestuia. Deoarece înălțimea aripioarelor dintr-un FinFET nu este variabilă, singura modalitate de a spori Weff-ul în cazul tranzistoarelor actuale este prin adăugarea mai multor aripioare în tranzistor. Așadar, în cazul unui FinFET, Weff-ul se poate dubla sau tripla, dar nu se poate crește cu 25% sau scădea cu 20%. Cu toate acestea, în cazul unui dispozitiv cu nanosheeturi, lățimea acestora poate fi ajustată, astfel încât un circuit poate fi compus din tranzistoare cu proprietăți diferite.

„Recent, proiectanții se confruntă cu multe provocări în ceea ce privește atingerea frecvenței maxime a dispozitivului cu un consum redus de energie. Datorită acestei flexibilități de proiectare, SRAM poate fi îmbunătățit foarte mult”, a declarat Song.

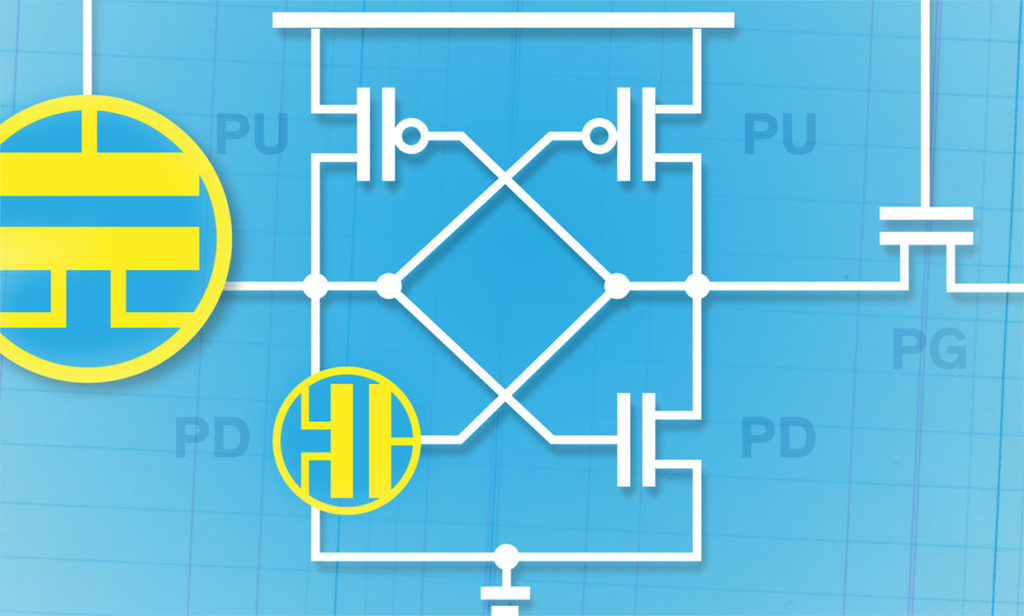

Song și echipa sa de proiectanți au profitat de această flexibilitate pentru a îmbunătăți performanța unei posibile generații viitoare de SRAM. SRAM este o celulă de memorie cu șase tranzistoare, utilizată predominant ca memorie cache în cadrul procesoarelor. De asemenea, aceasta este una dintre cele mai dense circuite ale unui cip logic. Samsung a testat două scheme de proiectare pentru a îmbunătăți marja de scriere a SRAM, adică tensiunea minimă necesară pentru a comuta starea celulei. Această valoare a fost obținută printr-o suprasolicitare a cipului, deoarece interconexiunile acestuia au fost micșorate și rezistența lor a crescut în consecință.

Cei șase tranzistori din cadrul SRAM pot fi împărțiți în trei perechi: porțile de trecere, tranzistoarele pentru „pull-ups” și pentru „pull downs”. În cadrul designului FinFET, Weff-ul tuturor celor trei tipuri de perechi este egal. Însă, în cadrul dispozitivelor cu nanosheeturi, echipa de proiectanți ai Samsung a fost liberă să facă diverse modificări, precum mărirea Weff-ului porților de trecere și a tranzistoarelor pull-down, sau mărirea Weff-ului porților de trecere și scăderea Weff-ului tranzistoarelor pull-down.

Scopul a fost acela de a reduce tensiunea necesară pentru a scrie pe celula SRAM fără a produce o instabilitate a celulei, ce ar putea produce ratarea accidentală a unui bit. Cele două scheme de proiectare dezvoltate au exploatat aceste ajustări ale lățimii canalului, în special mărirea Weff-ului tranzistoarelor și porților de trecere și micșorarea Weff-ului tranzistoarelor pull-down, pentru a crea o celulă SRAM care scrie la o tensiune cu 230 mV mai mică decât în mod normal.

Se preconizează ca Samsung va trece la un proces de fabricație a tranzistoarelor MBCFET pe 3 nm în anul 2022.